孙凝晖院士谈芯片未来形态和发展问题

发布时间 :2023年12月26日 18:39:20 关键词:

集成芯片是通过半导体微纳工艺将若干芯粒再次集成的技术,以形成较单芯片更高集成度、更丰富功能的芯片和系统。随着摩尔定律的发展逐渐放缓,集成芯片与芯粒技术在高性能芯片的制造与设计中发挥着越来越重要的作用,是加快建设科技强国,实现高水平科技自立自强的重要引擎。

在国家自然科学基金委部署集成芯片重大研究计划的背景下,12月16日至17日,第一届集成芯片和芯粒大会在上海顺利举办,大会由复旦大学和中国科学院计算技术研究所共同主办,主题为“跨学科探索集成芯片前沿技术”。大会主席、中国工程院院士、中国科学院计算技术研究所孙凝晖在会上作了重要报告,回顾了集成芯片的发展历程,总结了集成芯片所面临的科学问题,并对集成芯片发展的趋势作了展望。

集成芯片发展历程

集成芯片发展的初衷是应对超级计算的需求。孙凝晖院士指出,计算机的发展和芯片技术的发展几乎是一一对应的:半导体基础构件经历了电子管、分离晶体管、平面集成晶体管、超大规模集成晶体管、3D集成晶体管,计算机系统也随之实现算力狂飙,从最初只有385FLOPS的低算力计算机成长为算力超1000PFLOPS的超级计算机。孙院士提到,希望在2035年前能够研制出Z级计算机,这样的计算系统所需要的芯片基础构建是什么?这个问题已成为下一代半导体技术发展的重要驱动力。

提升芯片性能的三条主流技术路径

孙凝晖院士在会上总结了目前提升芯片性能的三条主流技术路径,这三条路径相辅相成,共同推动芯片升级迭代。

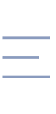

经典摩尔定律:目前,通过晶体管尺寸微缩提高集成度依然是发展主线,单die的CPU性能受光刻面积和工艺节点的制约,同等芯片面积下,工艺节点是算力的决定因素。然而当前国际先进制程尺寸已逼近物理极限,技术发展趋缓,并且当下我国仍面临着光刻机禁令的限制,短期内难以破解EUV光刻机瓶颈,实现7nm以下工艺难度很大,而通过扩展众核规模的方式提高CPU性能又会受到良率的限制。

新原理器件:在摩尔定律逐渐放缓的情况下,发展新原理器件、研发新材料,提升单个晶体管器件性能逐渐成为业界共识。孙院士指出,新原理器件目前还仅限于专用高端领域的应用计算,并且因其从研究到应用的周期较长,需提前部署。基金委2019年发布“后摩尔时代新器件”重大研究计划,从器件电子学、物理新机制、新材料体系、仿生电子学全方位推进新器件基础研究和架构创新。

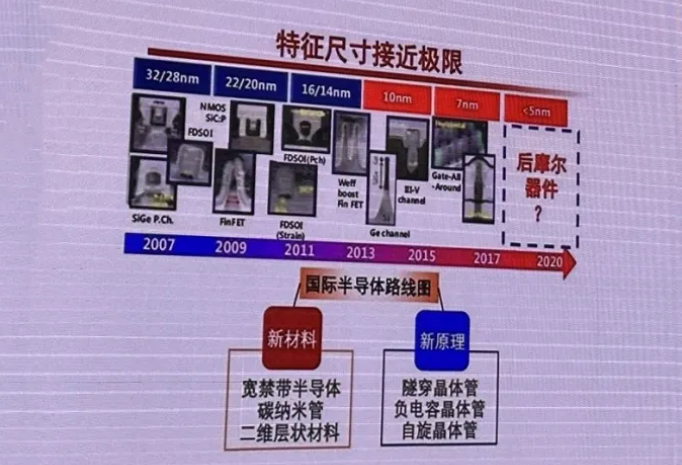

集成芯片:孙院士表示,从计算系统的角度来看,扩大规模不仅可以在微观电路层面,更可以在终端芯片层面。传统芯片是大量晶体管在二维平面上集成制造而形成的,而集成芯片是先将晶体管集成具有特定功能的芯粒/Chiplet,再将预制好的芯粒照需求用制造技术三维集成为芯片。这样做的优势是可以大幅提高晶体管总量,并且芯粒的模块化可以降低芯片设计生产成本。

集成芯片是一条使用现有自主工艺实现高性能芯片的变革性技术途径,例如采用14nm工艺可实现7nm,甚至5nm工艺的芯片性能,既可缓解当下需求危机,又可与另两条路径相辅相成。

现有芯片设计范式是从晶体管到芯片,自下而上地堆叠,这样的范式伴随着两个原生问题:v复杂系统的转变。集成芯xc片的“构造法”是引入了系统工程学理念,自上而下进行分解、组合和集成,将大幅降低设计难度。

集成芯片的科学问题

芯粒的数学描述和组合优化理论:少量芯粒集成时映射关系简洁,而将复杂功能分解到大量芯粒时,需要借助数学运算;传统集成电路针对微观晶体管的数学描述不适用于芯粒尺度,更需建立新的数学理论。孙院士提出的研究思路与传统芯片中采用布尔代数表示晶体管功能不同,采用函数理论对多芯粒系统进行抽象描述,并基于复杂函数的分解优化建立对集成芯片的芯粒最优分解的建模和分析。

孙院士提到,要重点关注以下三个方面:

集成芯片的抽象数学描述

设计复杂空间建模、降阶与与优化理论

跨层次、随机、不可精确计算函数的优化

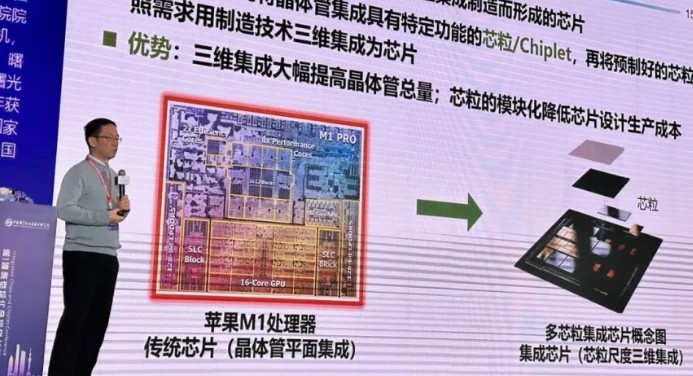

大规模芯粒并行架构和设计自动化:随着芯粒的数量和种类大幅提升,怎样应对芯片设计复杂度的爆炸式增长成为必须应对的重要问题。目前集成芯片的芯粒种类少、数量少,可调整的设计参数有限,并行设计的难度较低,而大规模芯粒集成时就要考虑分解效率、三维自动化布局布线等新问题,需要EDA工具完成。

孙院士指出,现有EDA用于以晶体管为单元的平面电路设计,可作为以芯粒为单元的三维EDA的开发基础。现行商业化EDA工具主要基于模型/暴力搜索等方法实现自动化。针对集成芯片,可引入专家知识+人工智能协同的新方法取代传统方法,构建多芯架构体系和集成芯片EDA工具的优化算法,提升设计效率。在这一问题上,孙院士指出要重点关注多芯并行体系结构和互连接口、集成芯片的综合和布局布线算法、多芯并行的编译原理与软件栈。

芯粒尺度的多物理场耦合机制与界面理论:

孙院士表示,少量芯粒集成时仅需在二维层面分析电、热、力传导,距离远耦合度低,效应易预测,而大规模芯粒集成时扩展到三维空间,多层堆叠结构带来复杂界面的物理量传导锅合问题,并且传统集成电路对微观晶体管电热力传导建立的物理模型,已不适用于芯粒尺度的预测分析宏观热理论。因此不同功能和种类的芯粒在形成界面时,如何优化电、热传导,避免应力破坏,是集成芯片面临的第三大科学问题。

孙院士在会上提到的研究思路是需以芯粒作为连接微观与宏观的核心枢纽,以微观物理理论为基础构建芯粒尺度的多物理场、多界面耦合的快速、精确的仿真计算方法。在此过程中应重点关注电-热-应力交互的多物理场仿真、大功率集成芯片的电源管理与散热理论以及3D互连界面的可靠性与容错设计。

集成芯片发展的趋势和现状

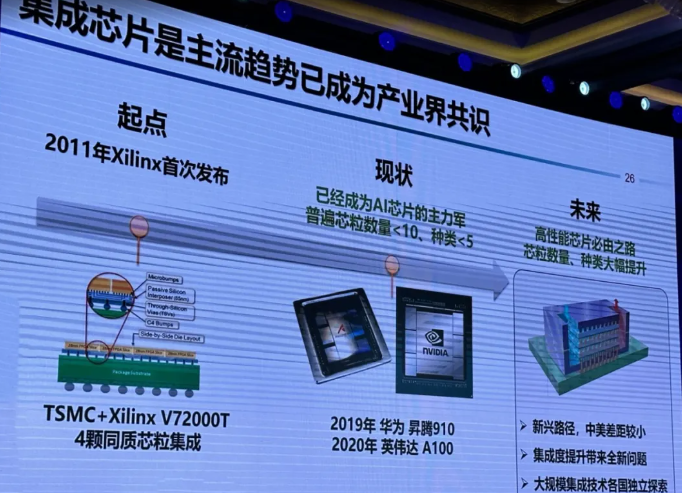

在致辞最后一部分,孙院士提到,当下,集成芯片是芯片架构的主流趋势已成为产业界的共识。在这条新兴路径上,中美差距较小,各国也在独立探索集成度提升带来的全新问题。互联和接口标准的制定是当前产业界关注的重点,也是集成芯片生态构建的重要基石。我国在全球生态构建上还是处于比较弱势的地位,因此需要构建开放、开源的芯片生态。

2023年7月,国家自然科学基金委发布“集成芯片前沿技术科学基础”重大研究计划,以集成规模持续提升为主要目标,以科学问题为牵引,以企业出题的技术难题为抓手,发布白皮书,制定路线图,提到能开源的要开源,建立统一的开源生态。对此孙凝晖院士表示,集成芯片的科学研究需要和企业界紧密结合在一起,由企业界出题,学术界答题,同时也需要具有微电子、半导体、计算机、材料、数学等交叉专业背景的技术人员一起进行集成芯片技术的研究。

“集成芯片前沿技术科学基础”重大研究计划聚焦在集成芯片中芯粒集成度、大幅提升后带来的全新问题,需要汇聚多方面智慧,发挥各自领域特长,充分交流碰撞,才能发展出一条基于自主集成电路工艺提升芯片性能新技术路径。

推荐新闻

-

2026-01-08

CES 2026:英伟达Rubin架构首曝光,告别单芯片时代! 查看详情 查看详情 -

2025-12-09

关于晶圆代工,这可能是今年最全面的 查看详情 查看详情 -

2025-11-25

存储超级周期来袭:谁在承压、谁在突围? 查看详情 查看详情 -

2025-11-25

第二十二届中国国际半导体博览会在京开幕,同期举办第七届全球IC企业家大会 查看详情 查看详情