D2D互连,升级重塑!

发布时间 :2024年08月05日 18:00:09 关键词:

2024年7月18日,美国国防部高级研究计划局(DARPA)向德克萨斯电子研究所(TIE)注入了高达8.4亿美元的巨额资助。这笔资金不仅是对TIE科研实力的高度认可,更是DARPA加速推进其下一代微电子制造(NGMM)计划的重要里程碑。此次资助聚焦于研发3D异质集成(3DHI)技术,并赋予军用Chiplet前所未有的生命力。DRAPA的这一重磅布局,无疑是对Chiplet技术未来发展潜力的再次有力印证。

遵循摩尔定律的辉煌历程,芯片制造商曾每18个月便能通过工艺迭代实现性能翻倍。然而,当技术前沿触及3nm、2nm乃至更细微的边界时,进步的步伐显著放缓。继续提升晶体管密度即便在技术上可行,也会带来巨额成本。当靠工艺提升性能遭逢瓶颈,单芯片设计的技术路线难以为继,基于Chiplet的芯片设计技术转型,成为许多芯片产业链头部玩家的共识。

Chiplet更高的可扩展性、灵活性和成本效益给芯片行业带来了转机,同时也带来了新的挑战,特别是在芯片到芯片(Die-to-Die,D2D)通信方面。

芯粒互连是指在同一物理载体内不同的功能芯粒之间的互连,是延续摩尔定律的重要技术。它类似于一个高效运作的企业内部,不同专业部门间通过紧密无间的协作,共同推动整体战略目标的实现。每个芯粒承载着特定的功能角色,而它们之间的无缝互连则确保了系统整体的流畅运行与性能飞跃。为实现多样化芯粒生态中的高效互连,需要在芯片封装层面确立互连互通的统一标准,定义芯粒之间通信和数据交换的具体规则,即通用芯粒互连技术,也就是D2D互连接口协议。它相当于企业间或部门间为确保高效协作而采用的通用语言与沟通标准(如国际通用的商务语言、标准的文档格式等)。它的引入,极大地降低了芯粒间通信的复杂性,提升了系统的兼容性与可扩展性。

串行互连

串行互连技术以其IO数量少、传输距离远和速度快等优势,在D2D互连中占据重要地位。SerDes通过差分信号传输方式实现数据的高速传输,具有功耗低、抗干扰强等特点。随着技术的不断进步,SerDes技术被细分为多种类型,如长距(LR)、中距(MR)、短距(VSR)、极短距(XSR)和超短距(USR)SerDes,以满足不同应用场景的需求。

在Chiplet技术兴起之前,串行互连技术已在系统或芯片间的高速互连中广泛应用。然而,随着Chiplet技术的发展,对D2D互连的带宽、延迟和能效提出了更高的要求。因此,SerDes技术也在不断优化和创新,以适应Chiplet系统的需求。例如,XSR SerDes和USR SerDes等新型技术应运而生,它们具有更低的功耗、更小的面积和更灵活的通信协议,非常适合于Chiplet之间的短距离高速互连。

并行互连

与串行互连相比,并行互连技术通过多条并行通道同时传输数据,具有更高的带宽和更低的延迟。然而,并行互连也存在一些缺点,如需要更多的IO资源和更复杂的布线设计。在Chiplet技术中,并行互连技术同样占据一席之地。特别是对于一些对带宽和延迟要求极高的应用场景,如高性能计算(HPC)和人工智能(AI)等,并行互连技术能够提供更优的性能表现。

然而,随着Chiplet技术的不断发展,并行互连技术也面临着一些挑战。例如,随着芯片尺寸的减小和封装密度的增加,并行互连的布线难度和成本也在不断增加。此外,并行互连还需要依赖先进的封装技术来实现高效的信号传输和散热管理。

在Chiplet技术蓬勃发展的背景下,统一芯粒互连(Universal Chiplet Interconnect Express,UCIe)标准应运而生,成为D2D互连领域的焦点。UCIe是由多家行业领军企业和标准化组织共同发起的一项开放标准,旨在通过定义统一的物理层、协议层和管理层规范,实现不同厂商Chiplet产品之间的无缝互连。

相比于以往的标准,UCIe具备以下几点优势:

可满足异构集成的需求

现代芯片设计越来越多地采用异构集成,即在同一系统中集成来自不同工艺节点或不同供应商的不同类型的芯片(如CPU、GPU、存储器等)。UCIe协议提供了一种标准化的互连方式,方便不同芯片间的高效通信。

可满足模块化设计的需求

UCIe促进了模块化设计,使得芯片设计可以更加灵活和可扩展。设计者可以选择最合适的芯片模块(chiplets)进行组合,而不是从头开始设计整个系统。

可提高带宽和性能

随着数据密集型应用(如AI、机器学习、大数据分析等)的兴起,对高带宽和低延迟的需求不断增加。UCIe协议旨在提供高带宽和低延迟的芯片间互连,满足现代计算需求。

可降低成本和提升经济性

通过使用标准化的互连协议,可以降低设计和制造成本,并缩短产品上市时间。设计者不再需要为每个项目开发定制的互连解决方案。

可提升可靠性

UCIe协议包含了详细的测试和验证规范,提供了一套完整的测试方法和工具,确保互连的可靠性和性能。其标准化的测试流程简化了故障检测和诊断过程。

UCIe标准的推出,对于推动Chiplet技术的普及与应用具有重要意义。它不仅简化了Chiplet系统的设计与集成过程,降低了技术门槛和成本,还促进了Chiplet生态系统的繁荣发展。UCIe作为Chiplet技术发展的产物,正引领着D2D互连技术的新一轮变革。

面对全球Chiplet技术的浪潮,中国并未缺席。尽管众多中国半导体企业已跻身UCIe联盟,但在标准制定的核心舞台上,我们缺乏足够的决策影响力。尤为关键的是,UCIe框架尚不足以直接解决国内芯片企业面临的深层次技术挑战。

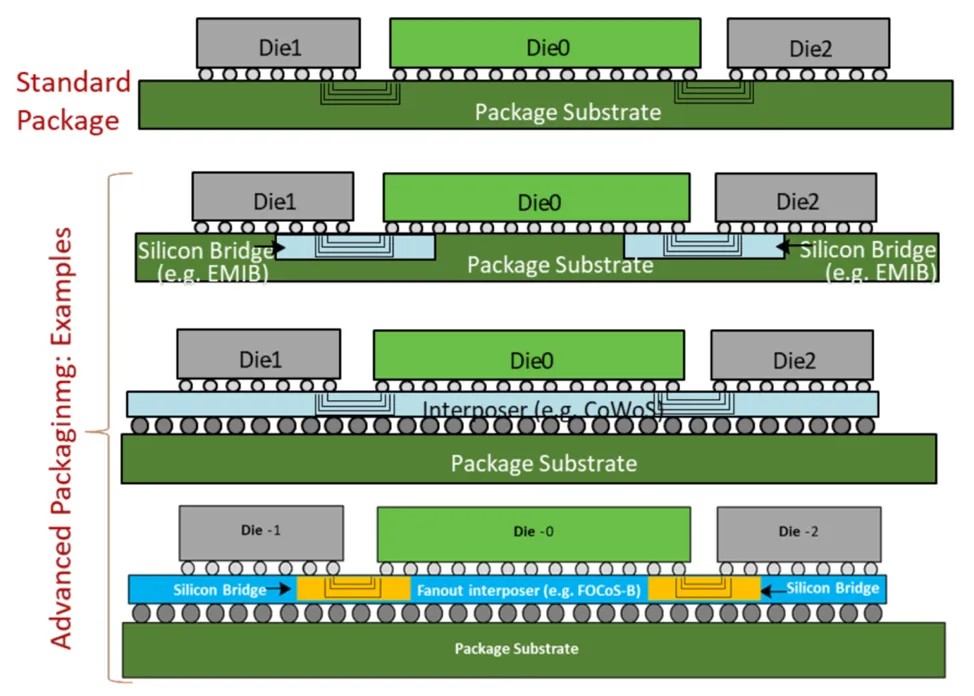

深入剖析UCIe所支持的标准封装和先进封装技术,不难发现标准封装作为入门级别,其应用范畴受限于非高性能需求的芯片领域。至于UCIe所提及的三大尖端封装技术——英特尔的EMIB、台积电的CoWoS以及日月光的FoCoS-B,当前中国大陆的制造基地尚不具备直接支持能力。这意味着,若遭遇技术封锁,大陆企业依托UCIe协议,或将被迫退守标准封装领域,导致Chiplet间的互连带宽大幅缩减至先进封装技术的1/6,性能损失显著,难以满足高端应用的需求。

UCIe支持的封装技术

鉴于国内封装技术正以惊人的速度积累与革新,构建一套能够广泛兼容各类先进封装技术、具有更强自主性的中国Chiplet标准,对于构建稳健、可控的Chiplet生态系统至关重要。

为此,中国计算机互连技术联盟(CCITA)已迈出坚实步伐,主导制定了《小芯片接口总线技术要求》这一中国首个原生Chiplet技术标准。该标准的发布实施,标志着中国在Chiplet技术领域取得了重要突破,对于推动中国集成电路行业延续摩尔定律、突破先进制程工艺限制具有里程碑式的意义。

展望未来,中国Chiplet D2D互连标准的自主发展之路虽充满挑战,但前景光明。相信在不久的将来,中国将在全球Chiplet生态中占据举足轻重的地位。

推荐新闻

-

2026-01-08

CES 2026:英伟达Rubin架构首曝光,告别单芯片时代! 查看详情 查看详情 -

2025-12-09

关于晶圆代工,这可能是今年最全面的 查看详情 查看详情 -

2025-11-25

存储超级周期来袭:谁在承压、谁在突围? 查看详情 查看详情 -

2025-11-25

第二十二届中国国际半导体博览会在京开幕,同期举办第七届全球IC企业家大会 查看详情 查看详情